##1.寄存器

通用寄存器可保存数据和地址,是arm架构工作的基本存储单元。

ARM处理器共有37个寄存器:

- 31个通用寄存器,包括程序计数器PC。这些寄存器是32位。

- 6个状态寄存器。这些寄存器是32位的,但只使用了其中的12位。

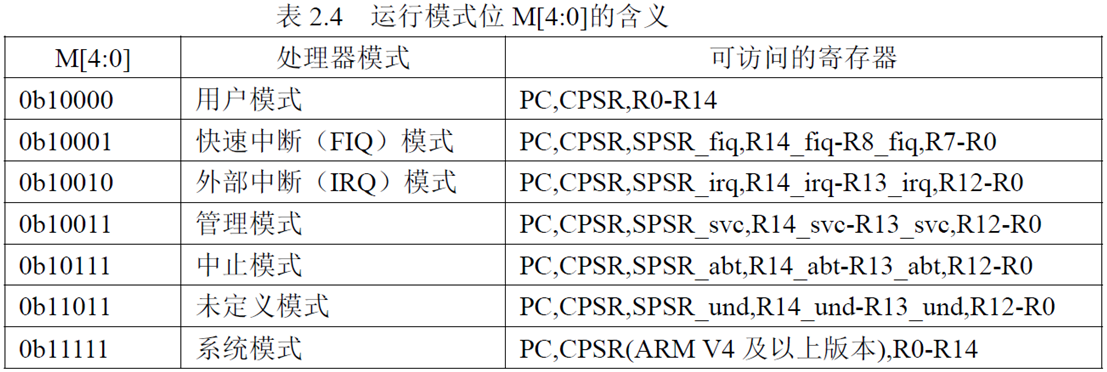

这些寄存器不能被同时访问,具体哪些寄存器是可编程访问的,取决于微处理器的工作状态及具体的运行模式,寄存器安排成部分重叠的组,每种处理器模式使用不同的寄存器组。

##2.工作模式与寄存器组织 ###2.1通用寄存器 通用寄存器(R0—R15)可以分为三类:未分组寄存器R0—R7,分组寄存器R8—R14,程序计数器PC(R15)。 1)未分组寄存器R0—R7。对于每一个未分组寄存器来说,在所有的处理器模式下指的都是同一个物理寄存器。在异常中断造成处理器模式切换,由于不同的处理器模式使用相同的物理寄存器,可能造成为分组寄存器中数据被破坏。未分组寄存器没有被系统用于特别的用途,任何可采用通用寄存器的场合都可以使用未分组寄存器。 2)分组寄存器R8—R14。指同一个寄存器名,在ARM微处理器内部存在多个独立的物理寄存器,每一个物理寄存器分别与不同的处理器模式对应,如表2.1所示。

表2.1 ARM状态下的寄存器组织

| 用户模式 | 系统模式 | 管理模式 | 数据访问终止模式 | 未定义指令终止模式 | 外部中断模式 | 快速中断模式 |

|---|---|---|---|---|---|---|

| (usr) | (sys) | (svc) | (abt) | (und) | (irq) | (fiq) |

| R0 | R0 | R0 | R0 | R0 | R0 | R0 |

| R1 | R1 | R1 | R1 | R1 | R1 | R1 |

| R2 | R2 | R2 | R2 | R2 | R2 | R2 |

| R3 | R3 | R3 | R3 | R3 | R3 | R3 |

| R4 | R4 | R4 | R4 | R4 | R4 | R4 |

| R5 | R5 | R5 | R5 | R5 | R5 | R5 |

| R6 | R6 | R6 | R6 | R6 | R6 | R6 |

| R7 | R7 | R7 | R7 | R7 | R7 | R7 |

| R8 | R8 | R8 | R8 | R8 | R8 | R8_fiq |

| R9 | R9 | R9 | R9 | R9 | R9 | R9_fiq |

| R10 | R10 | R10 | R10 | R10 | R10 | R10_fiq |

| R11 | R11 | R11 | R11 | R11 | R11 | R11_fiq |

| R12 | R12 | R12 | R12 | R12 | R12 | R12_fiq |

| R13 | R13 | R13_svc | R13_abt | R13_und | R13_irq | R13_fiq |

| R14 | R14 | R14_svc | R14_abt | R14_und | R14_irq | R14_fiq |

| PC | PC | PC | PC | PC | PC | PC |

| CPSR | CPSR | CPSR | CPSR | CPSR | CPSR | CPSR |

| SPSR_svc | SPSR_abt | SPSR_und | SPSR_irq | SPSR_fiq |

对于分组寄存器R8—R12,每个寄存器对应两个不同的物理寄存器,当使用fiq模式时,可以访问R8fiq—R12_fiq;当使用除fiq以外的其他模式时,可以访问R8_usr—R12_usr。

对于R13,R14,每个寄存器对应6个不同的物理寄存器,其中的一个是用户模式和系统模式共用的,另外5个物理寄存器对应于其他5种不同的运行模式。采用下面的记号来区分不同的物理寄存器:

R13

寄存器R13在ARM指令中常用作堆栈指针SP,但这只是一种习惯用法,用户也可以使用其他的寄存器作为堆栈指针。 由于处理器的每种运行模式均有自己独立的物理寄存器R13,在用户应用程序的初始化部分,一般都要初始化每种模式下的R13,使其指向该运行模式的栈空间,这样,当程序运行进入异常模式时,可以将需要保护的寄存器放入R13所指向的堆栈,而当程序从异常模式返回时,则从对应的堆栈中恢复,采用这种方式可以保证异常发生后程序的正常执行。 寄存器R14又称做子程序链接寄存器或链接寄存器LR,在ARM体系中具有两种作用: 第一种作用,每一种处理器模式自己的物理R14都存放当前子程序的返回地址。当通过BL和BLX指令调用子程序时,R14自动被设置成该子程序的返回地址。在子程序返回时,R14的值复制回程序计数器R15中,完成子程序返回。具体实现可以使用下列两种方法之一: 执行如下其中一条指令:

MOV PC , LR

BX LR

在子程序入口处使用以下指令将R14存入堆栈:

STMFD SP!, {<register>, LR}

相应的,下面的指令可以实现子程序返回:

LDMFD SP!, {<register>, PC}

第二种作用,当异常中断发生时,该异常模式特定的物理R14被设置成异常模式将要返回的地址,对于有些异常模式,R14的值可能与将返回的地址有一个常数的偏移量,对于不同的异常模式,这个偏移量会有所不同。具体的返回方式与上面的子程序返回方式基本相同。 另外,R14寄存器也可以作为通用寄存器使用。

3)程序计数器PC(R15) 寄存器R15用于程序计数器(PC)。在ARM状态下,由于ARM指令是字对齐的,所以PC的第0位和第1位总为0;在Thumb状态下,PC的第0位是0。PC虽然可以作为一般的通用寄存器使用,但是有一些指令在使用R15时有一些特殊规则。当违反了这些限制时,该指令执行的结果将是不可预料的。 由于ARM体系结构采用了流水线制(以三级流水线为例),对于ARM指令集来说,PC指向当前指令的下两条指令的地址,即PC的值为当前指令的地址加8个字节。

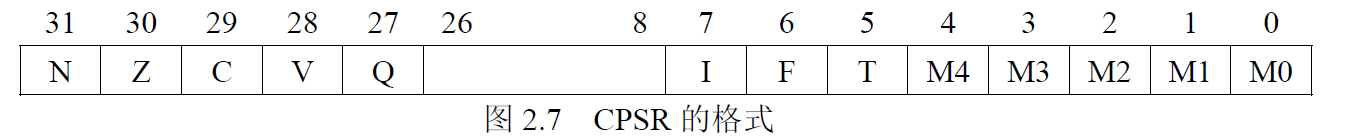

###2.2程序状态寄存器 ARM体系结构包含1个当前程序状态寄存器(CPSR)和5个备份的程序状态寄存器(SPSR)。 CPSR(Current Program Status Register)可在任何运行模式下被访问,它包括条件标志位、中断禁止位、当前处理器模式标志位,以及其他一些相关的控制和状态位,如图2.7所示。

每种异常模式下都有一个对应的物理寄存器一备份的程序状态寄存器SPSR(Saved Program Status Register)。当异常发生时,SPSR用于保存CPSR当前值,从异常退出时,则可由SPSR来恢复CPSR。用户模式和系统模式不属于异常模式,他们没有SPSR,当在这两种模式下访问SPSR,结果是未知的。

-

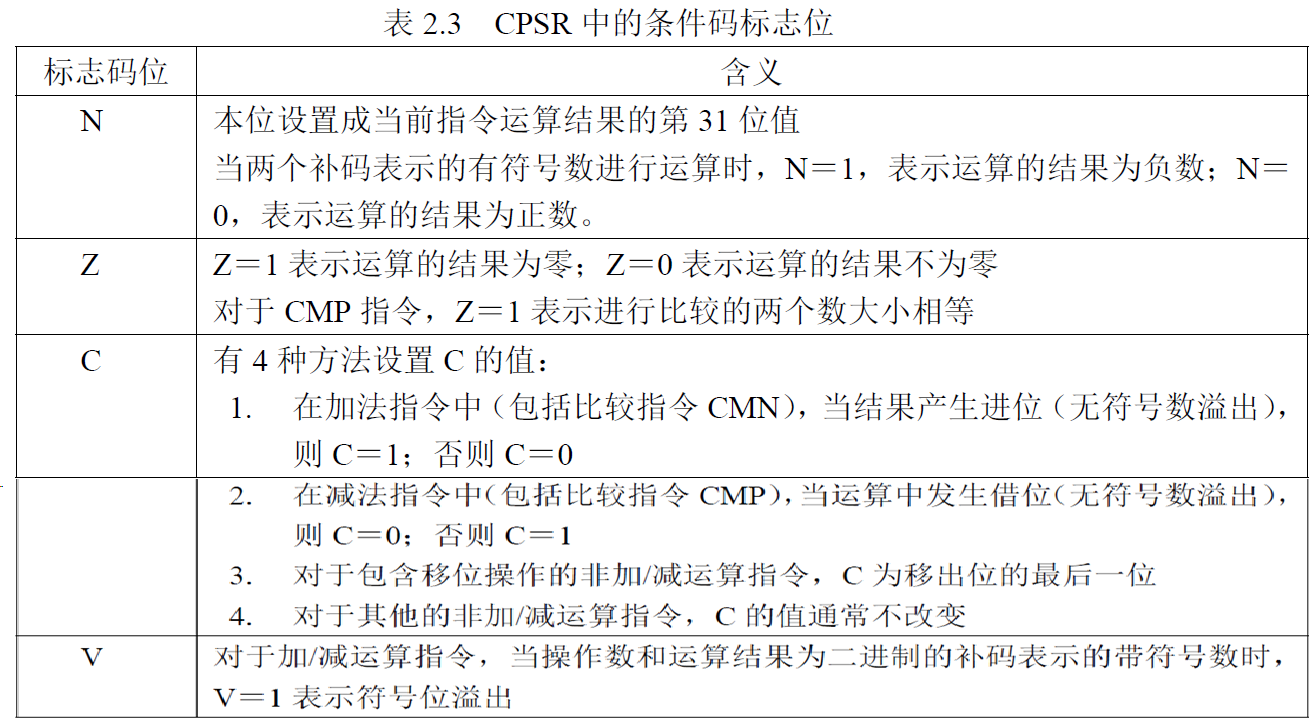

条件码标志(28-31位) N、Z、C及V统称为条件码标志位。其内容可被算术和逻辑运算的结果所改变,由此可以决定某些指令是否被执行。具体含义如表2.3所示。

-

Q标志位(第27位) 在ARM V5及以上版本的E系列处理器中,用Q标志位指示增强的DSP运算指令是否发生了溢出。在其他版本的处理器中,Q标志位无定义。

-

CPSR的控制位(第7-0位) CPSR的低8位(包括I、F、T和M[4:0])称为控制位,当发生异常时这些位可以被改变。如果处理器运行特权模式,这些位也可以由程序修改。

-

中断禁止位I,F: I=1禁止IRQ中断 F=1禁止FIQ中断

-

T标志位:该位反映处理器的运行状态 对于ARM体系结构V4及以上的版本的T系列处理器,当该位为1时,程序运行与Thumb状态,否则运行于ARM状态。 对于ARM体系结构V5及以上的版本的非T系列处理器,当该位为1时,执行下一条指令以引起未定义的指令异常;当该位为0时,表示运行于ARM状态。

-

运行模式位M[4:0]:M0、M1、M2、M3、M4是模式位。这些位决定了处理器的运行模式。具体含义如表2.4所示。

4.其他的位为保留位,用作以后的扩展。